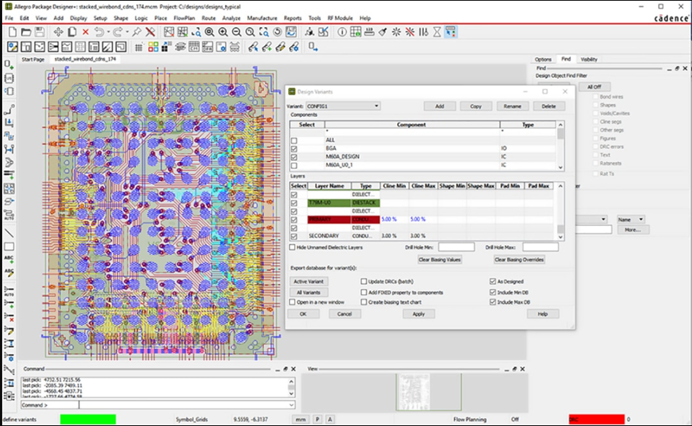

Allegro X SiP Layout Option

Allegro X Advanced Package Designer SiP Layout Option专为应对系统级封装(SiP)实施挑战而生,高效集成高引脚数芯片至单基板。该技术支持设计师轻松实现复杂多芯片组装的探索、捕捉与优化,并实现两大关键集成。无缝对接 Cadence Innovus技术,优化芯片/封装互连,深度集成 Virtuoso技术,赋能射频模块设计。

模块优势

- 增强型多芯片集成:为高性能封装技术提供高引脚数芯片的单基板高效集成方案;

- 连接驱动设计:加速关键互连(如DDR内存与高速串行接口)的规划、优化与时序收敛;

- 自动交互与布线:提供复杂互连快速设计工具,包含基于 Specctra引擎 的硅基基板自动布线;

- 接口感知设计:通过分层设计能力加速标准化接口布线,采用代表总线与接口的 "流程化"模式,简化分配与布线操作;

- 全面支持DesignTrue DFM技术与ARC:提供完备的 DesignTrue可制造性设计规则 与装配检查,提升基板良率并预防制造缺陷;

- 实时可制造性规则:通过直观电子表格界面实时定义与应用可制造性规则,优化设计流程;

- 设计与工艺变量管理:创建支持多配置的主设计模板,实现不同堆叠与键合方案的评估。

Allegro X SiP Layout Option功能

-

物理布局优化方案

防错型设计数据库,物理设计规则实时DRC检查,电气约束同步验证;

-

全方位布线解决方案

约束驱动推挤式交互布线,自动交互布线功能,全自动布线引擎;

-

实时设计规则检查

集成Allegro X DesignTrue DFM规则检查,凭借无与伦比的灵活性、尖端技术及全面分析工具,重塑行业效率与创新标准;

-

高级连接模型支持

灵活支持网表/原理图连接,提供动态连接("On-the-Fly" Connectivity)生成能力;

-

3D线缆与设计规则可视化检查

突破传统设计局限,在沉浸式3D环境中可视化执行复杂线缆与设计规则检查;

-

先进硅基布局方案

提供局部精密金属密度调控工具,有效控制超薄封装(500-1000µm)翘曲问题;

-

金属密度平衡工具

通过网格化金属层与焊盘,实现跨设计金属密度全局平衡;

-

高性能GDSII掩模处理

释放GDSII掩模处理的业界标杆能力——PCB与半导体器件制造的关键环节;

-

物理验证系统(PVS)无缝集成

与工艺设计套件(PDK)规则库直接对接,构建革命性设计验证与签核平台;

-

完整扇出型晶圆级封装(FOWLP)支持

为Fabless公司IC后端团队及封装基板设计师提供覆盖设计→验证全流程方案,紧密对接IC制造工艺;

-

高效SiP与先进封装开发

实现复杂多芯片/分立基板组件的设计探索→捕获→构建→优化→验证全流程集成;

-

接口感知设计

采用分层式接口感知技术加速DDRx/HBM/显卡/高速串行总线协议实现,同步提升设计质量、性能与可靠性;

-

早期设计探索与权衡分析

超前干预机制确保潜在问题在演变为高成本故障前被识别解决,显著节省时间与资源;

-

设计左移与协同优化

完成I/O焊盘环/阵列协同设计,实现IC-基板-系统多层级优化,支持双向工程变更(ECO)与版图-原理图比对(LVS)流程,提供设计优化可行性验证;

-

台积电集成扇出封装(InFO)技术支持

通过Cadence芯片级与封装设计工具集成,为InFO技术提供增强型无缝设计流程,缩短整体交付周期;

-

单元级电源完整性

支持全面电迁移与IR压降(EM-IR)设计规则验证,提供全芯片片上系统(SoC)电源签核精度保障;